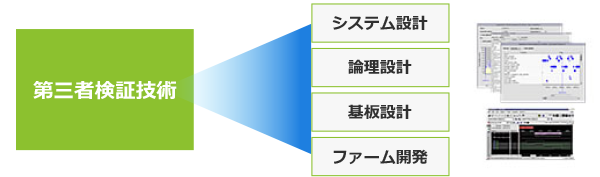

LSI · FPGA 設計業務

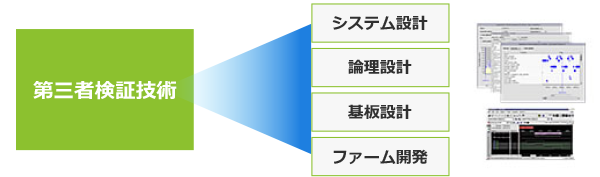

当社のコアコンピタンスである第三者検証技術を用いて、高品質なLSI・FPGA・基板設計サービスを提供します。 近年の、微細化・高集積化・高速化・低消費電力化・短TAT化などの要求に応えるべく、当社は今後もこうした設計環境のさらなる高度化を継続し、お客様に高品質な製品とサービスを提供してまいります。

お客様のご要望に合わせて、お客様事務所での常駐、または弊社持ち帰りのいずれでも対応致します。

お客様のご要望に合わせて、お客様事務所での常駐、または弊社持ち帰りのいずれでも対応致します。

開発環境

| ■上位設計言語 : SystemC、SystemVerilog |

| ■ハードウェア設計言語 : Verilog-HDL、VHDL |

| ■アサーション言語 : PSL、SVA |

| ■論理シミュレータ : IES、VCS、ModelSim |

| ■FPGA設計環境 : ISE、Vivado、Vivado-HLS、Synplify、Quartus II |

開発環境使用実績

| ■上位設計言語:SystemC、SystemVerilog | ■ハードウェア記述言語:Verilog-HDL、VHDL |

| ■高位合成ツール:Bluespec、Catapult、CtoS | ■論理合成ツール:DesignCompiler、RTLCompiler |

| ■RTLチェッカー:SpyGlass | ■非同期チェッカー:SpyGlass-CDC、Conformal-CDC |

| ■議論シミュレータ:IES、VCS、ModelSim | ■波形ビューア:Verdi、SimVision、DVE |

| ■アサーション言語:SVA、PSL | ■形式検証ツール:IEV |

| ■等価検証ツール:Formality、Conformal-LEC | ■STAツール:PrimeTime |

弊社所有ツール

| ■論理シミュレータ:IES、VCS、ModelSim |

| ■FPGA設計環境:Vivado、ISE、QuartusⅡ |

| ■波形ビューア:Verdi、SimVision、DVE |

| ■基板回路設計ツール:OrCAD |

SoC、FPGA設計・検証実績

| ■スマートフォン用SoC |

| ■デジカメ用SoC |

| ■複合機用SoC |

| ■基地局用FPGA |

アルゴリズム検証環境開発

「アルゴリズムは出来たけど実証が出来ていない」と悩まれていたらお声掛けください。

概略仕様やCソースなどから、実証環境を開発して提供いたします。

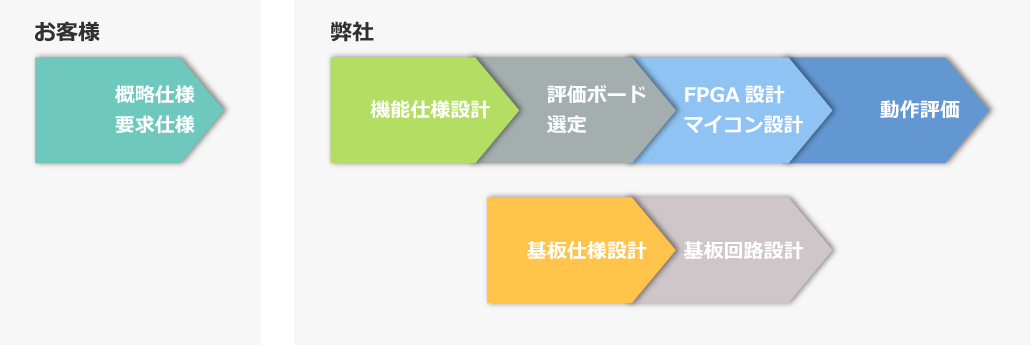

①お客様は、概略仕様、Cソースコード、ホワイトボードベースの仕様などをご提供ください。

②弊社で、実動作させるためのハードウェア仕様とファームウェア仕様を設計して、

機能をFPGA、マイコン、基板に分割して実装いたします。

アルゴリズム検証環境開発の流れ

使用するFPGAは、機能・性能とご予算に合わせて、最適なFPGAを選定します。

大規模FPGAでの高機能・高性能の実現や、小規模FPGAでの回路最適化・低予算化など、お客様のご要望に合わせて対応致します。

機能を実装するハードウェアは、市販の評価ボード、または弊社で設計する基板のどちらでも可能です。

市販の評価ボードだけでは機能が足りないとき、アドオンボードをお作りします。

開発例

1)高速画像処理による物体検知とトレース

実装技術例:高速カメラ処理、空間フィルタ、時間フィルタ、エッジ検出、魚眼補正、Bicubic法、オプティカルフロー、ステレオ処理

2)モータ制御

実装技術例:ベクトル制御、界磁巻線制御、非干渉制御、トルク制御、高調波補正

3)モータモデル

実装技術例:PMモータモデル、昇圧モデル、インバータモデル

主なFPGA開発実績

| ■Xilinx Virtex-5/6/7シリーズ |

| ■Xilinx Kintex-7シリーズ |

| ■Xilinx Zynq-7000シリーズ |

| ■Xilinx Spartan-6シリーズ |